Firebird 6502

A simple 8bit computer

Firebird is a simple 8 bit computer, based on a 6502 CPU, running at 1MHz. It has been designed specifically to act as a clock generator within the CBM 8032 AV project. It is planned to further enhance it with its own DAC & filter board for sound output, and maybe even some sort of graphics card.

Development Diary

21-02-04 first draft and tests of firmware using the CBM 8032 almost done: boot loader, display, initialisation of the VIA, ACIA, etc... front panel ordered at Schaeffer. Display panel PCB ordered. All parts for CPU board and power supply board ordered. Start to work on layout for CPU board.

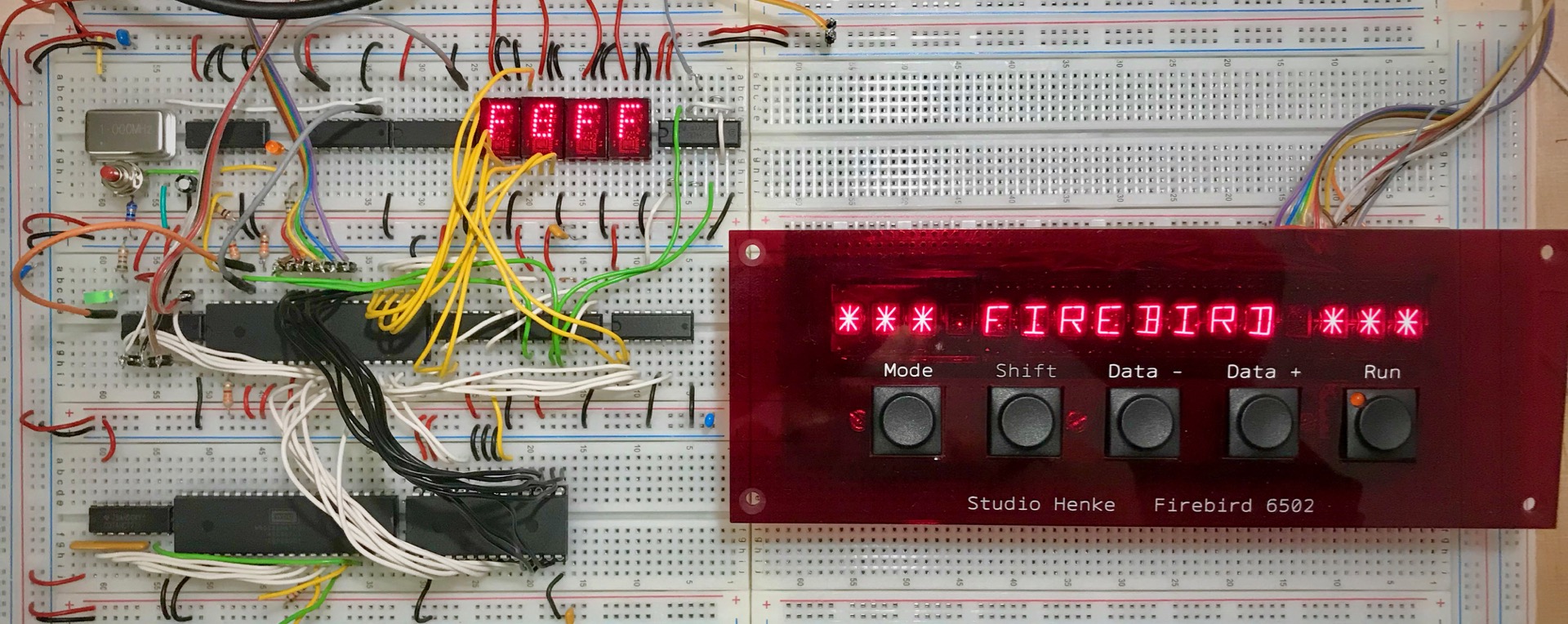

21-02-19 I guess I am going to test the complete system on the breadboard. Yesterday first successful run of a program. It now can write its name. Cute.

21-02-21 Struggling with bus timing and/or signal level issues.

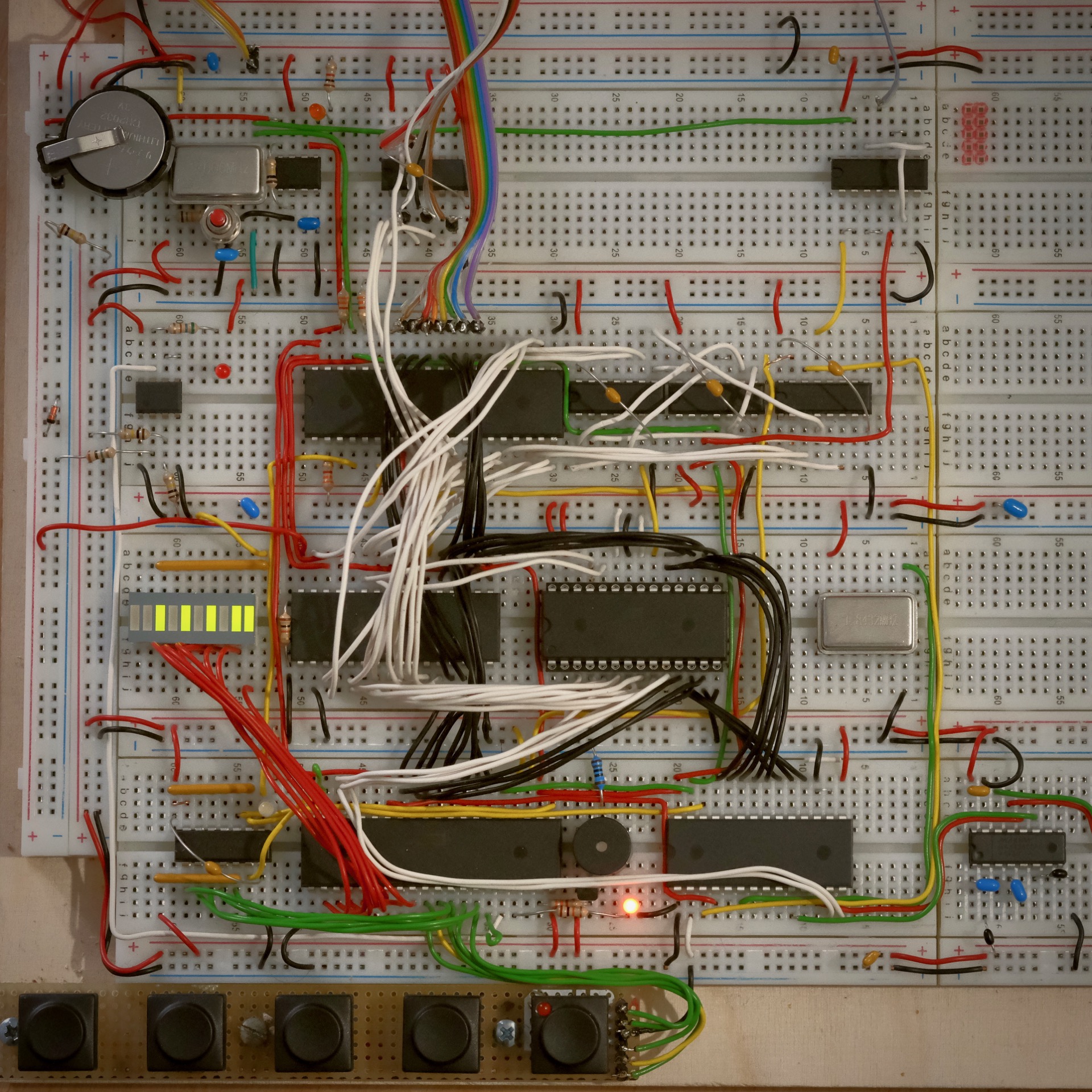

21-03-05 Found a really embarrassing logical error in my address decoding, which will probably explain the issues above... Will rip it all apart and redo with the new -hopefully correct- version. Start working on PCB design. Still aiming to get the machine into a 180mm x 65mm x 280mm enclosure. And having tons of ideas what to do with it once it is running fine.

21-03-10 CPU board is running 100% as expected, basic operating system is doing its job, and bidirectional data transfer between a Max patch and FiBi is also working flawless. Time to start working on the final print board.

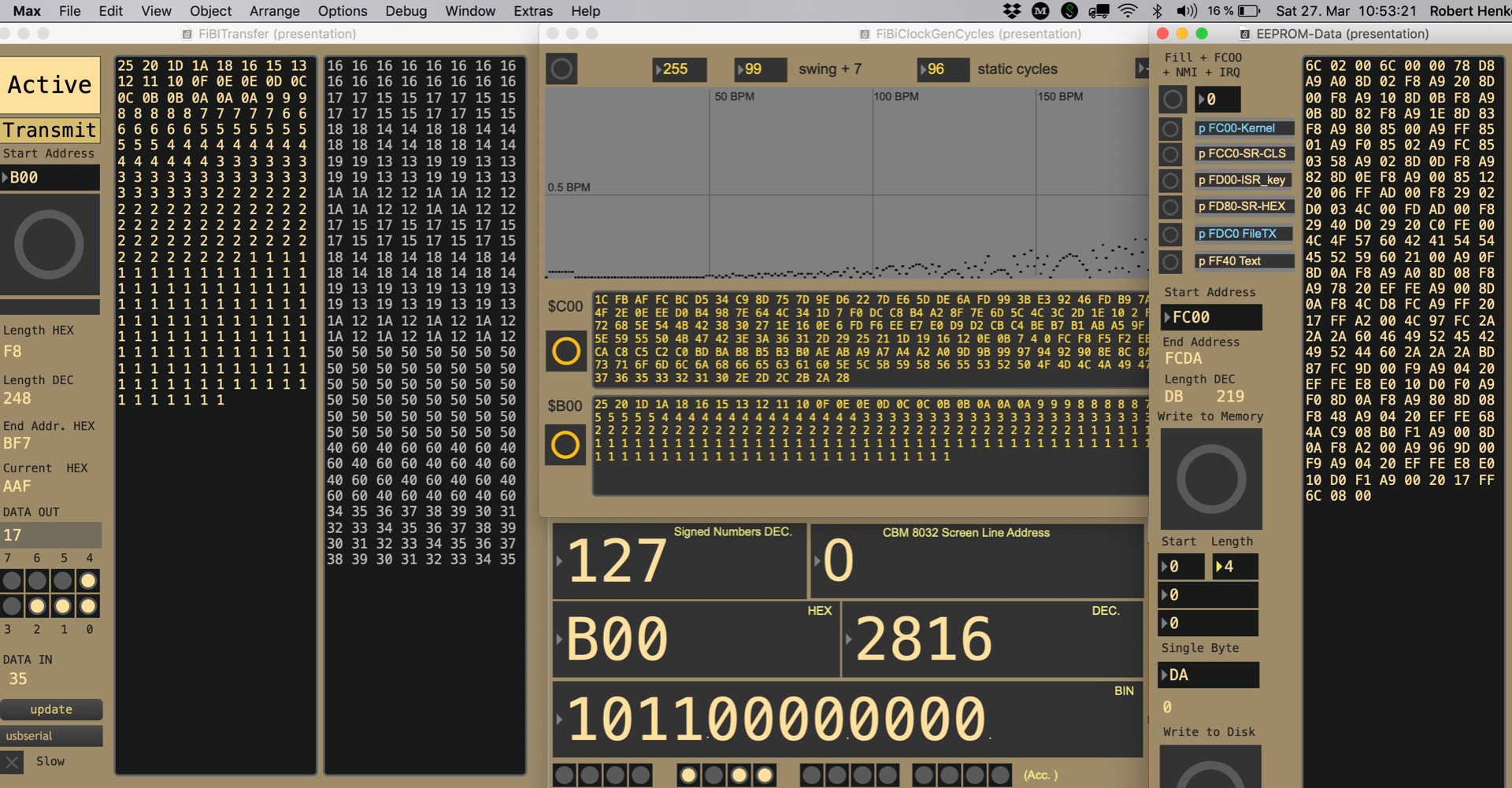

21-03-27 Building a lot of helper tools for this project. More work at the beginning, but so far paid of every single time, makes the process faster: A tool for data transfer from and to Firebird, a wait timer calculator for the Clock Generator software, a general purpose HEX - DEC - binary converter with some nice additions, and a tool to assemble program data and format for transfer to EPROM.

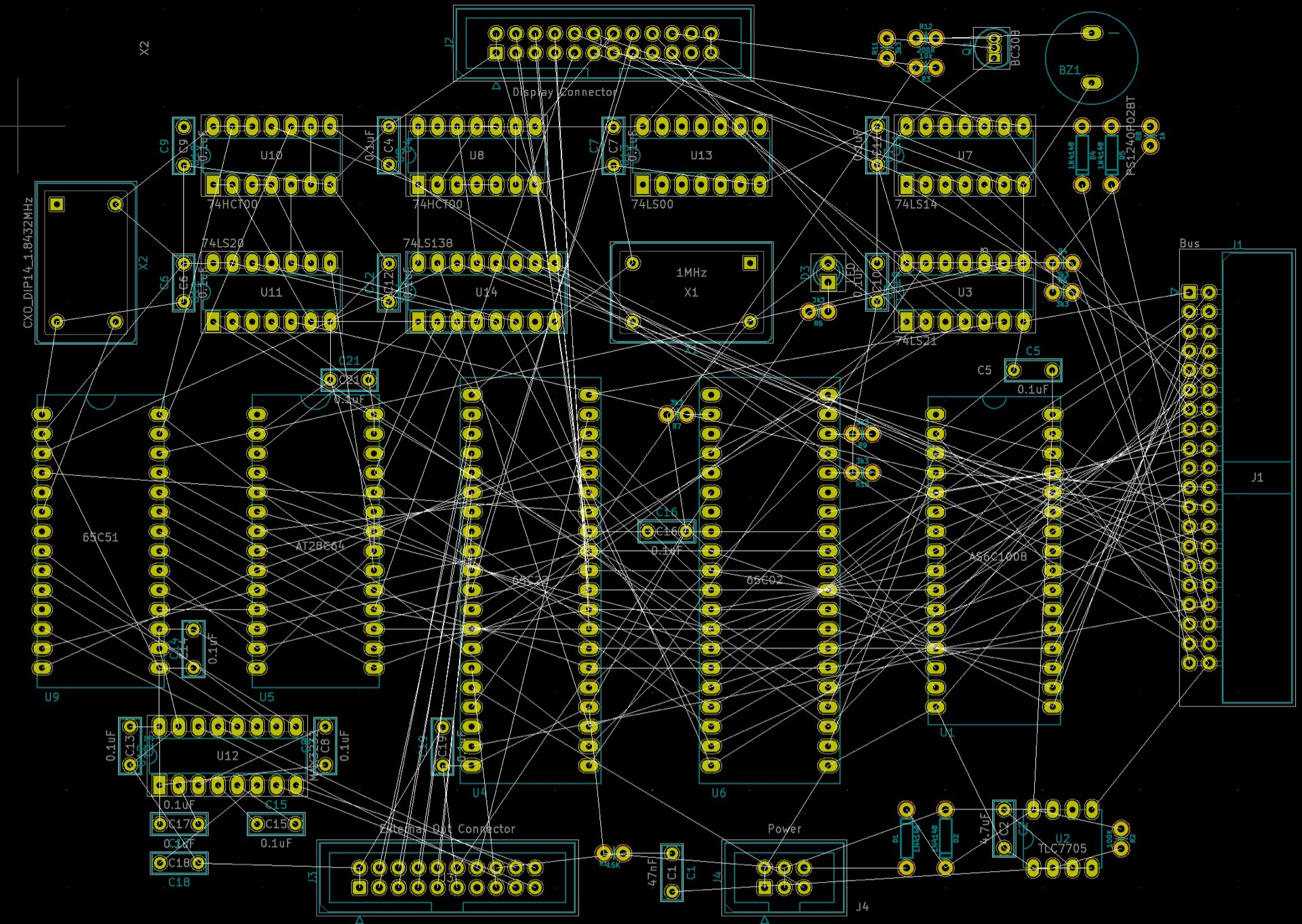

21-04-23 First serious attempt to design the PCB for the CPU board. A lot of details nailed down in the last four weeks, including adding a hardware key repeat function and solved a bus timing issue using a slower older 74LSxxx series chip in one place. Glad I bought a good logic analyser. It is absolutely fascinating to see that the breadboard version of this computer now just runs, and I am actually already using it to generate clock signals. Things move slower than I would want, but they are moving.

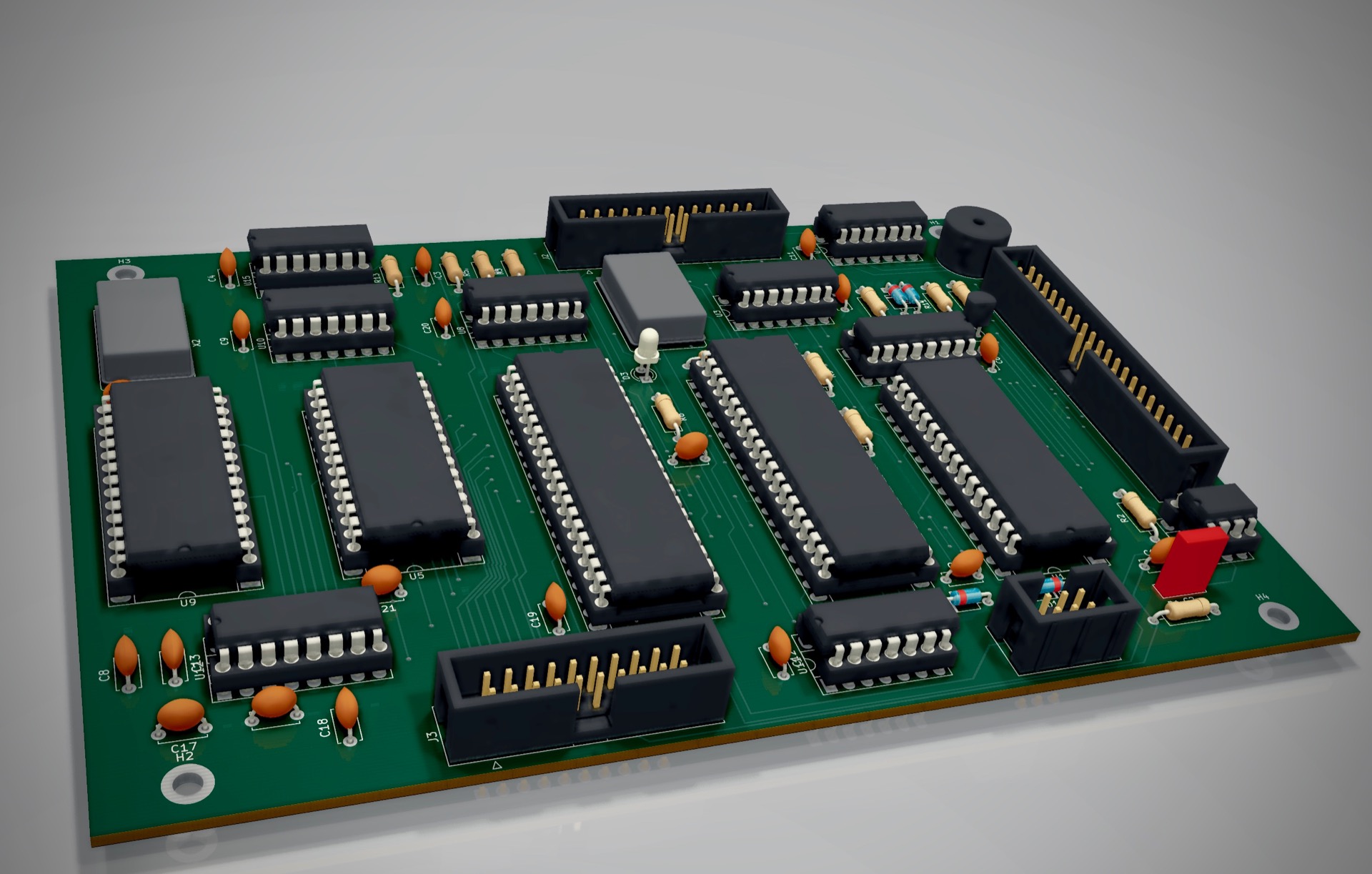

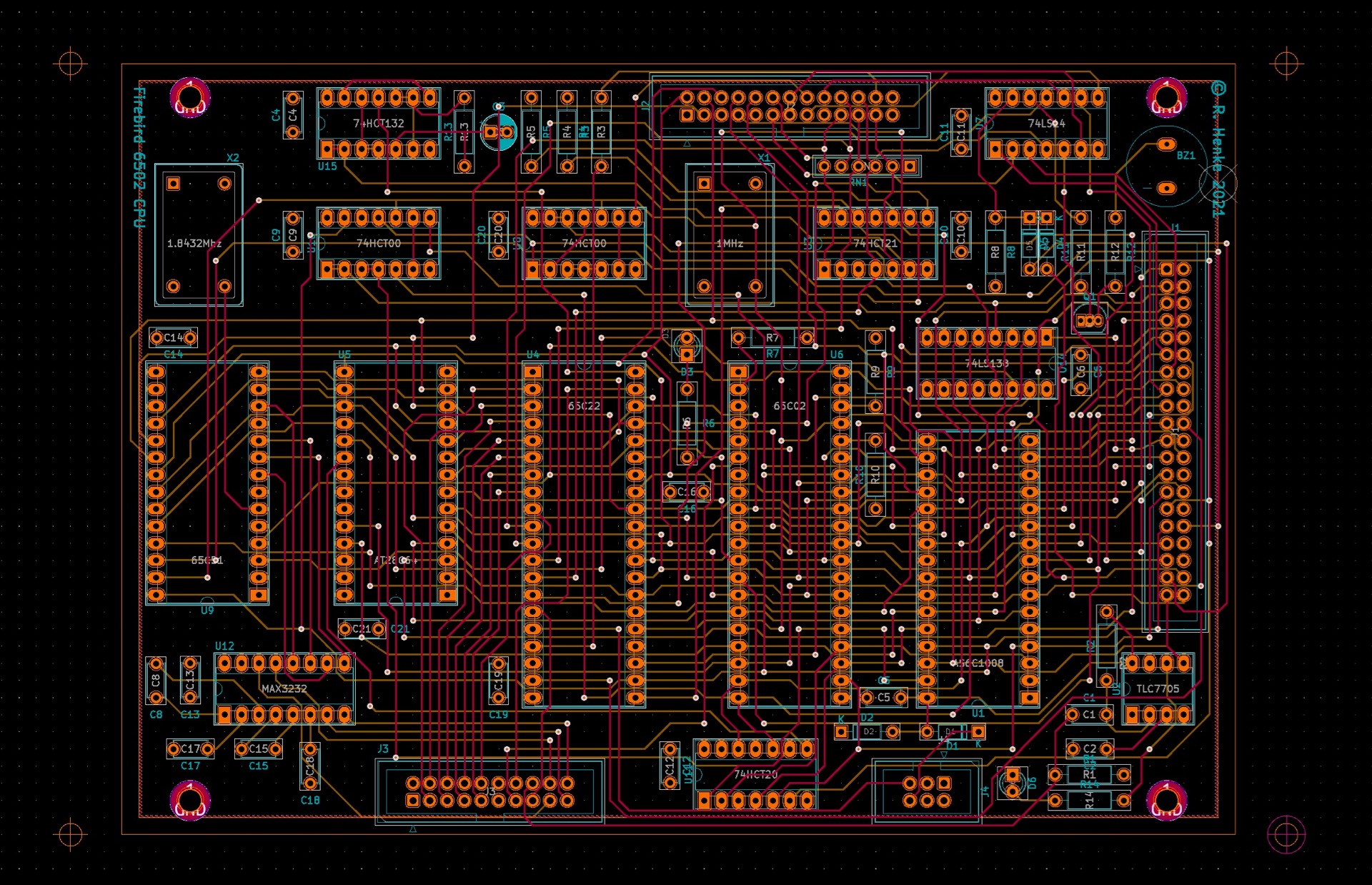

21-04-28 Spent the last days doing the circuit board routings manually in KiCad. Never done this before, so it took a while, but I am confident it is going to be good. Also correct 3D footprints of all parts now :-).

21-05-02 Still finding little things to improve / mistakes. Also making sure everything fits well together mechanically, connectors from CPU board to DAC board and to power supply need to be aligned, the big bus header connecting the boards needs to be in the right place, and such things more. Found an issue that would have drained the RAM backup battery faster than necessary. Solved it.

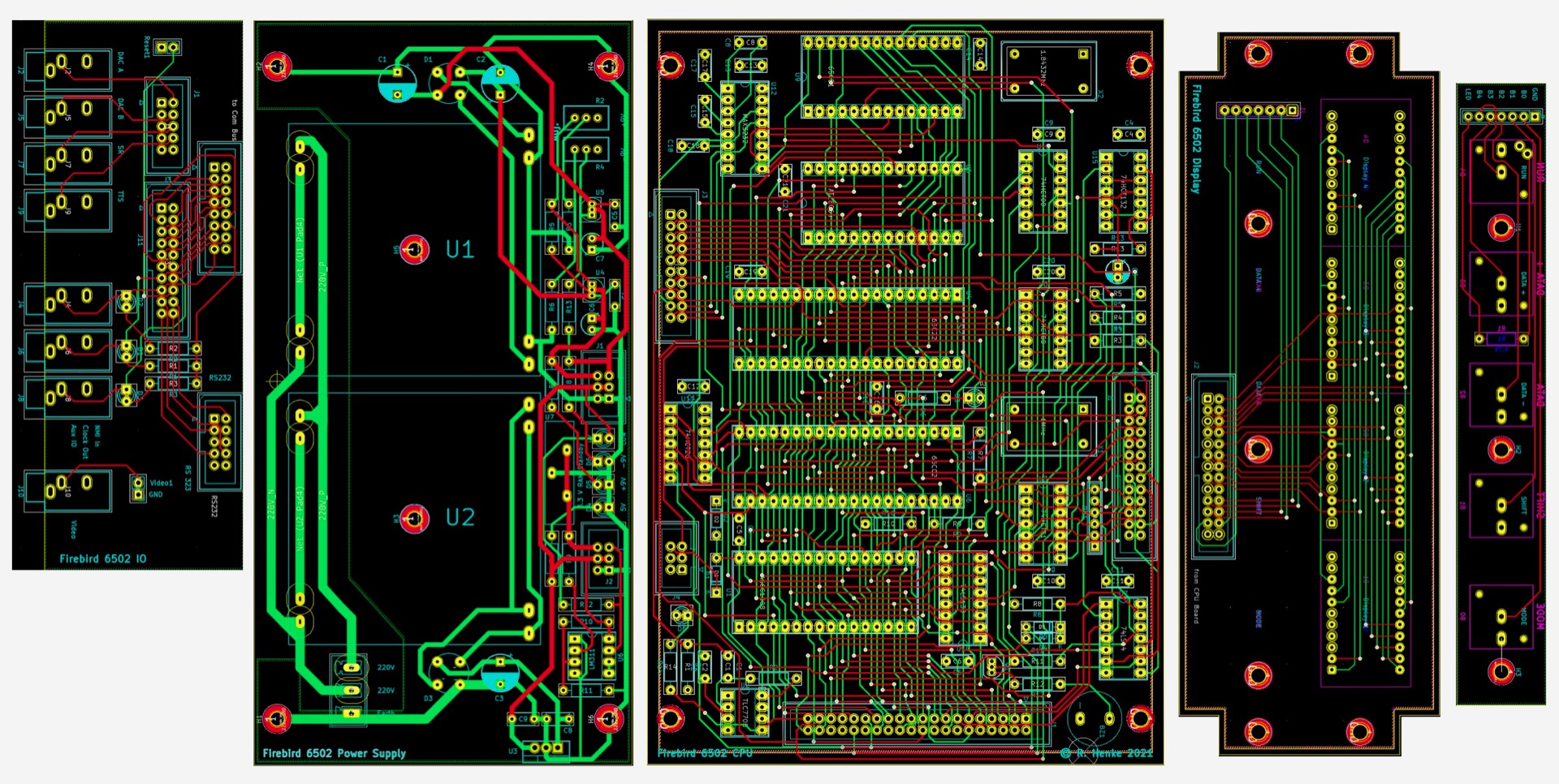

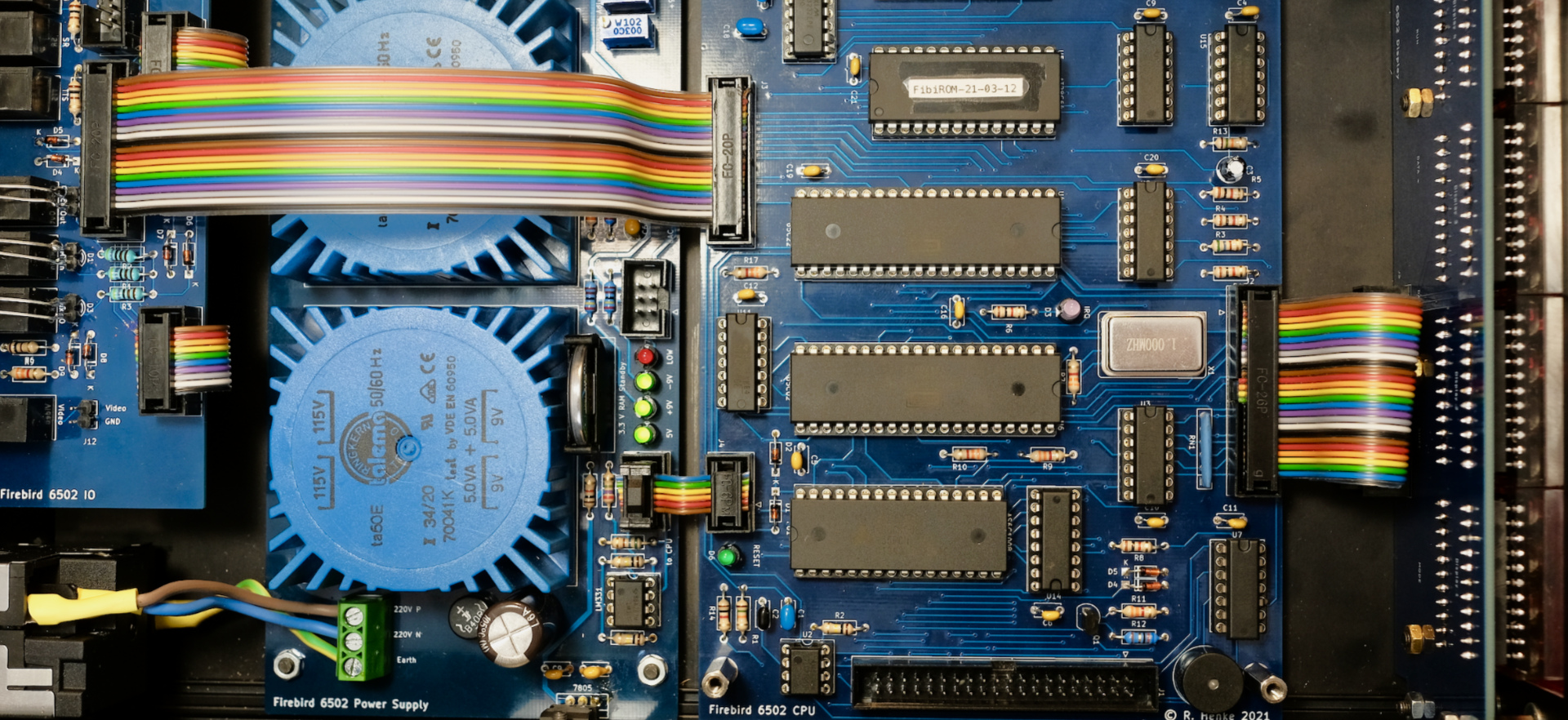

21-05-09 The six circuit boards which constitute the basic machine, from left to right: IO board, power supply board, CPU board, display board, button board. Not started yet is the development of the DAC / filter / (and potentially speech-synthesis) board, which is not necessary for its primary function as clock generator, but will be done eventually to allow me to develop sound routines for the CBM 8032 AV project on it.

21-07-24 Connections on the back for communication with the CBM 8032 computers and a serial port for interfacing with a MacBook.

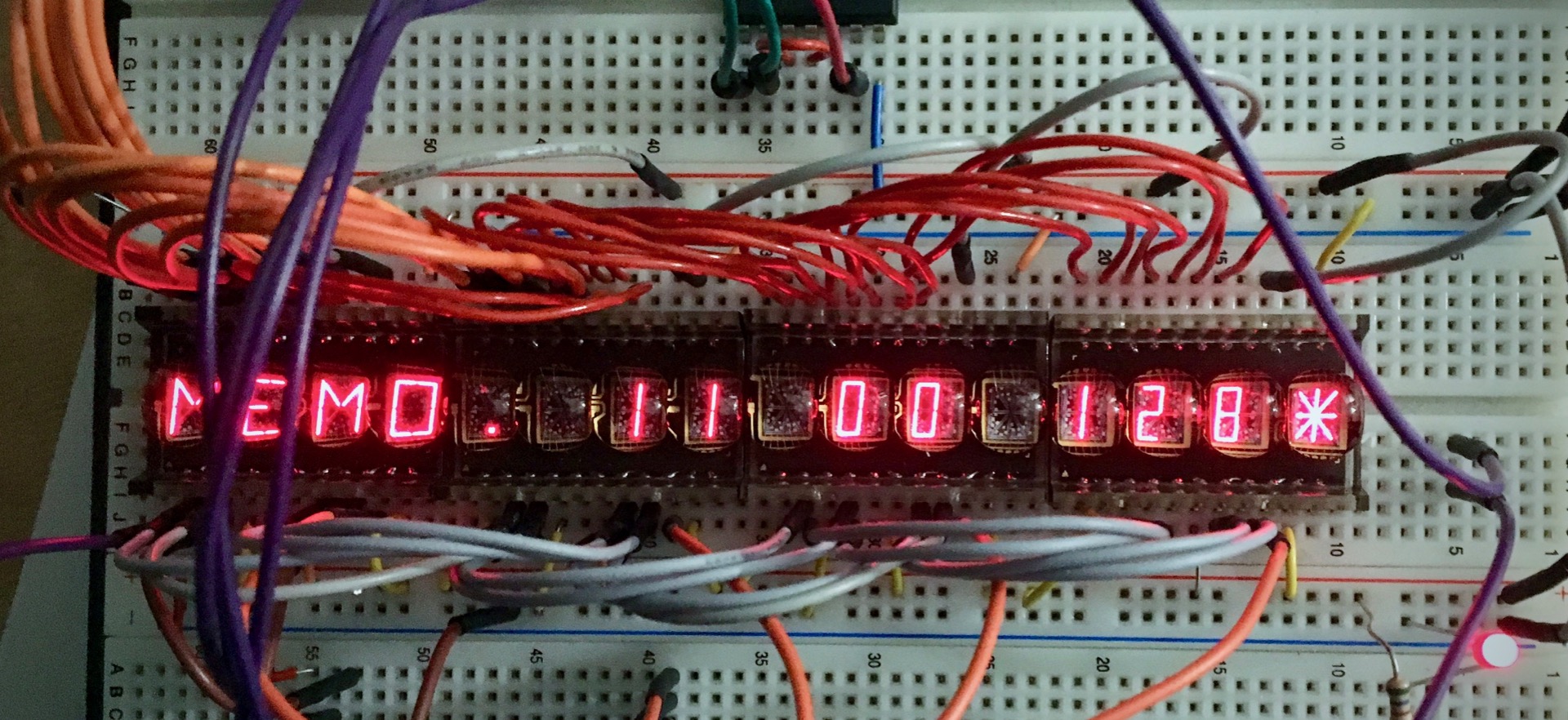

21-07-25 Self-test routine, notifies about memory corruption and other critical conditions.

From left to right: I/O board, power supply, CPU board, display board. Still missing is the audio DAC board and potentially a graphics / CRT control board, which will both sit on top of the CPU board.